计组上机总结

记录计组的一次上机实验,内容是存储器设计方面,考试设计题

实验名称:模型机的总体设计-存储器设计

一、实验目的

熟练掌握存储器的设计

二、实验要求

某机器中,已知ROM区域的地址空间起始地址为4000H开始,地址空间为8K * 16位(用8K * 8位的ROM芯片构成)。RAM采用最后地址8K*16位空间(用8K *8位的RAM芯片构成)。CPU采用8086、地址锁存器采用8282,数据缓冲器采用8286,译码器采用74ALS138。进行设计并用网络标签法完成要求:

- 画出地址译码方案

- 画出存储器与CPU等元件的连接图

三、实习步骤

首先分析题目所给的电路,题目中给的ROM地址空间起始地址为4000H,地址空间为8K16为,8k即2^13,即A0~A12

再分析RAM,由于RAM采用的是最后地址8K16为空间,因此同样是A0A12A15,因此可以先画出地址译码方案

题目中给定使用8086CPU,8086是16位微处理器芯片,相关信号如下:

CPU相关信号:

ALE:ALE 地址锁存允许信号(输出),高电平有效,不能被浮空。

一般用它来控制地址锁存器,它在下降沿会把地址锁存器的输入信号锁定,然后地址锁存器的输出用于提供地址。

一般在T1时刻出现ALE有效的信号,将地址送人地址锁存器。

RD 读信号引脚(输出),执行一个对内存货I/O端口的读操作,到底是读取内存中的单元数据还是I/O端口中的数据,取决于M/IO信号。

WR写信号(输出),低电平有效,对存储器或I/O写操作,具体哪种操作取决于M/IO信号。

M/IO存储器/输入/输出控制信号(输出)若此信号为高电平,表示CPU和存储器之间进行数据传输;

若为低电平,表示CPU和输入输出设备之间进行数据传输。

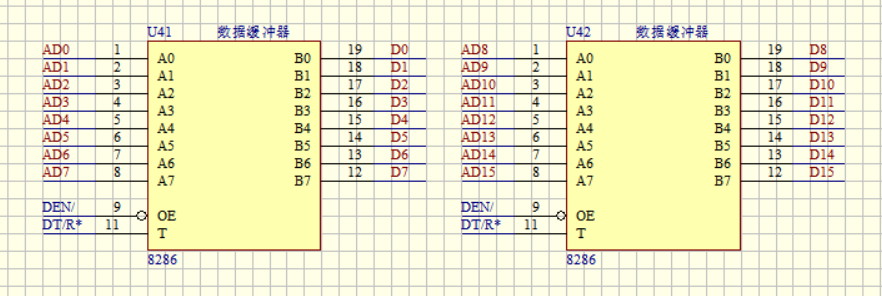

DEN信号:8086 CPU中,控制信号DEN的作用是.CPU发出的数据传输有效控制信号

DT/R信号:用来控制数据传送方向,在8086系统中,通常采用8286或8287作为数据总线的驱动器,用DT/R* 信号来控制数据驱动器的数据传送方向,当DT/R* =1时,数据驱动器进行数据发送;DT/R*=0时,数据驱动器进行数据接收。

因为是16位,所以地址为A0

A0A12为真正的地址,而A15A13对应于译码器的A,B,C

由于ROM地址空间为8k * 16位,所以依据题意需要采用2片8k * 8为的ROM芯片构成,在此选用两片2764芯片,基本参数如下:

A0到A12为13条地址信号输入线,说明芯片容量为2的13次方,即8K

D0到D7为数据线,表示芯片的每个存储单元存放一个字节(8位二进制数)。对芯片读数时,作为输出线,对芯片编程时,作为输入线。

CE为输入信号,低电平有效。(有称作片选信号)

OE为输出允许信号,低电平有效

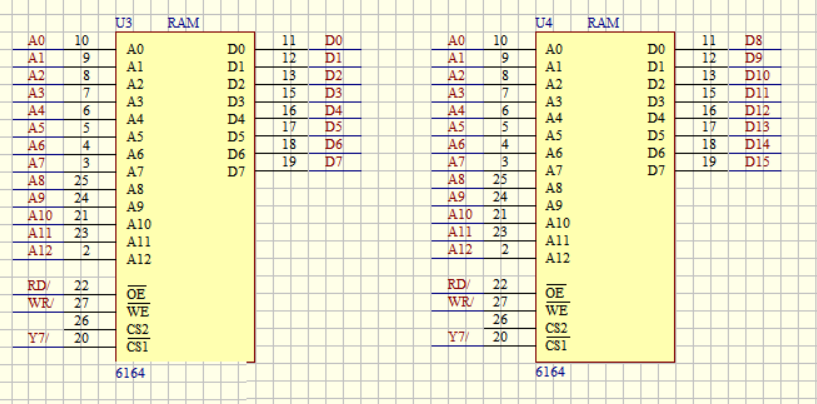

接着分析RAM芯片,同样是采用两个芯片进行片选,选择的芯片为SRAM6164芯片:

为8K×8bit的CMOSRAM芯片。

WE为写信号,CS为片选信号,OE为输出允许信号,D0D7为8位数据线,A0A12为13根地址线

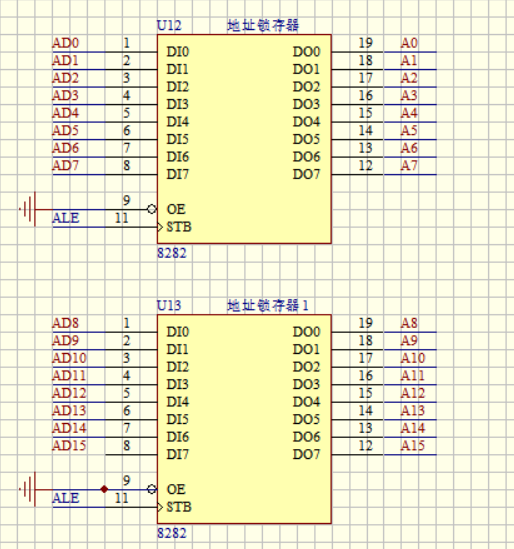

之后按照题目说的地址锁存器采用8282,关于地址锁存器相关概念不是很清楚,查阅后发现基本概念如下:

地址锁存器是一个暂存器,它根据控制信号的状态,将总线上地址代码暂存起来。8086/8088数据和地址总线采用分时复用操作方法,即用同一总线既传输数据又传输地址。当微处理器与存储器交换信号时,首先由CPU发出存储器地址,同时发出允许锁存信号ALE给锁存器,当锁存器接到该信号后将地址/数据总线上的地址锁存在总线上,随后才能传输数据。

数据缓冲器采用8286,数据缓冲器相关概念如下:

数据缓冲器是一款具有不同传输能力元件之间通过时用来暂存这些数据的存储器。

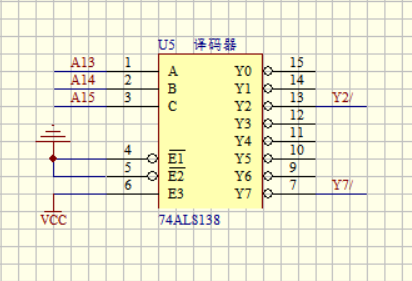

译码器采用74ALS138,根据输入的数字量在多个输出端中选一个有效,由之前的地址译码方案可知的当Y15,Y14,Y13分别为0, 1,0时,对应ROM地址,此时译码器的Y2端有效

同理RAM对应111,即Y7端有效